Domeniul proiectării de aplicații aerospațiale și de apărare este extrem de vast, cuprinzând sisteme portabile montate pe vehicule, nave maritime, aeropurtate și nave spațiale, precum și sisteme cu și fără echipaj uman, pentru aplicații tactice sau strategice. Proiectele din domeniul aerospațial și al apărării au multe lucruri în comun, cum ar fi necesitatea unei fiabilități ridicate în medii dificile pe durata misiunilor critice, însă fiecare tip de sistem prezintă propriile provocări unice.

Domeniul proiectării de aplicații aerospațiale și de apărare este extrem de vast, cuprinzând sisteme portabile montate pe vehicule, nave maritime, aeropurtate și nave spațiale, precum și sisteme cu și fără echipaj uman, pentru aplicații tactice sau strategice. Proiectele din domeniul aerospațial și al apărării au multe lucruri în comun, cum ar fi necesitatea unei fiabilități ridicate în medii dificile pe durata misiunilor critice, însă fiecare tip de sistem prezintă propriile provocări unice.

Este posibil ca proiectanții să fie nevoiți să se confrunte cu constrângeri puternice de putere pentru sistemele portabile sau cu constrângeri termice severe pentru sistemele amplasate în echipamente supuse la temperaturi ridicate sau fără ventilație forțată. Echipamentul final poate fi supus la șocuri sau vibrații extreme, la temperaturi extreme, la niveluri extreme de umiditate sau de umezeală sau la cantități extreme de radiații.

În afară de factorii de mediu, proiectanții de sisteme din domeniul aerospațial și al apărării trebuie, de asemenea, să depășească problemele legate de lanțul de aprovizionare, cum ar fi baza tot mai redusă de furnizori care sunt dispuși să investească în atingerea nivelurilor ridicate de calificare și certificare necesare pentru multe tipuri de sisteme aerospațiale și de apărare. În ultimii ani, numeroase programe guvernamentale de apărare au început, de asemenea, să acorde o atenție sporită fiabilității componentelor și proprietății intelectuale (IP) proiectate în sistemele pe care le achiziționează.

FPGA

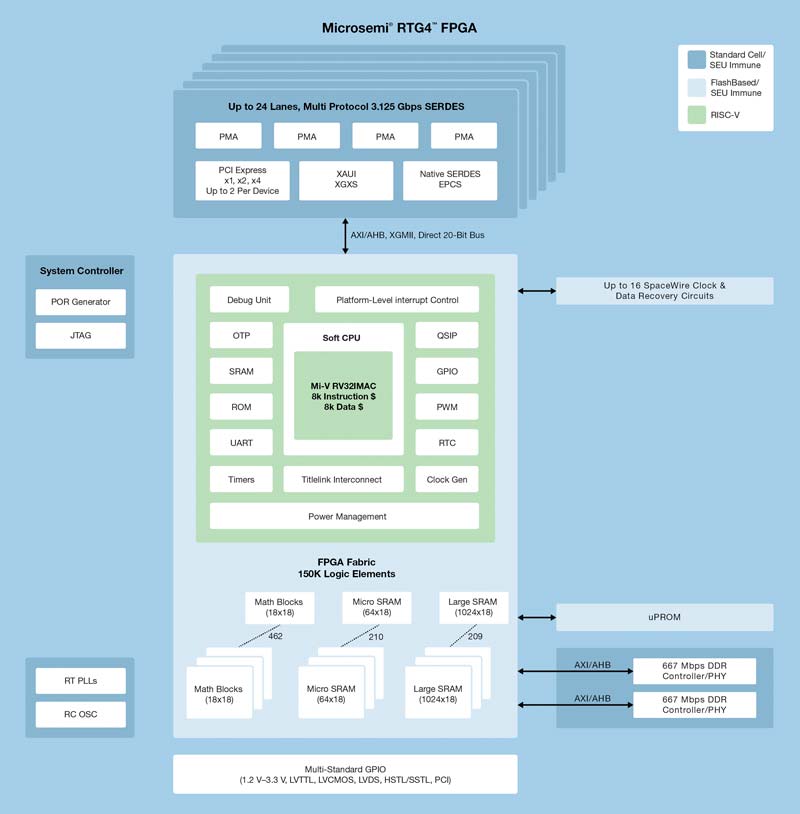

FPGA-urile (Field programmable gate array – arii de porți programabile) permit proiectanților să folosească platforme flexibile pentru integrare logică, care pot fi utilizate în toată gamă de proiecte aerospațiale și de apărare, abordând provocările enumerate mai sus. Multe sisteme de apărare depind de FPGA-uri pentru procesarea semnalelor de mare viteză, accelerarea hardware, extinderea I/O și procesarea embedded.

FPGA-urile (Field programmable gate array – arii de porți programabile) permit proiectanților să folosească platforme flexibile pentru integrare logică, care pot fi utilizate în toată gamă de proiecte aerospațiale și de apărare, abordând provocările enumerate mai sus. Multe sisteme de apărare depind de FPGA-uri pentru procesarea semnalelor de mare viteză, accelerarea hardware, extinderea I/O și procesarea embedded.

Cea mai flexibilă și mai adaptabilă abordare a procesării embedded în FPGA-uri utilizează nuclee de procesor soft IP. Avantajul utilizării unui nucleu soft IP pentru a implementa un microprocesor într-un FPGA este gradul ridicat de flexibilitate pe care îl oferă în comparație cu un procesor integrat, care este configurat permanent și nu poate fi modificat de către proiectant.

Un avantaj suplimentar al unui nucleu de procesor soft IP este disponibilitatea codului în limbaj de descriere hardware (HDL) pentru procesor, care permite proiectantului sau altor părți terțe să inspecteze procesorul IP pentru a se asigura că acesta conține doar logica necesară pentru a îndeplini funcția prevăzută, nici mai mult, nici mai puțin. Acesta este un principiu fundamental atât în ceea ce privește asigurarea proiectării, așa cum se întâmplă în aplicațiile aviației comerciale, cât și în ceea ce privește fiabilitatea, așa cum se întâmplă în anumite aplicații din domeniul apărării. Însă, o asemenea flexibilitate are un preț ridicat, deoarece majoritatea furnizorilor de IP pentru microprocesoare percep taxe foarte mari pentru furnizarea de versiuni HDL ale IP-ului lor pentru procesoare și aproape niciodată nu permit modificarea IP-ului în scopul optimizării.

Un avantaj suplimentar al unui nucleu de procesor soft IP este disponibilitatea codului în limbaj de descriere hardware (HDL) pentru procesor, care permite proiectantului sau altor părți terțe să inspecteze procesorul IP pentru a se asigura că acesta conține doar logica necesară pentru a îndeplini funcția prevăzută, nici mai mult, nici mai puțin. Acesta este un principiu fundamental atât în ceea ce privește asigurarea proiectării, așa cum se întâmplă în aplicațiile aviației comerciale, cât și în ceea ce privește fiabilitatea, așa cum se întâmplă în anumite aplicații din domeniul apărării. Însă, o asemenea flexibilitate are un preț ridicat, deoarece majoritatea furnizorilor de IP pentru microprocesoare percep taxe foarte mari pentru furnizarea de versiuni HDL ale IP-ului lor pentru procesoare și aproape niciodată nu permit modificarea IP-ului în scopul optimizării.

Apariția noii arhitecturi RISC-V cu set de instrucțiuni (ISA) pentru microprocesoare a adus proiectanților o mai mare libertate de a ajusta și optimiza microarhitectura astfel încât aceasta să satisfacă în mod optim nevoile programului lor de dezvoltare. De asemenea, aceasta permite proiectanților inspectarea completă a codului HDL în scopul asigurării și încrederii în proiectare, fără a suporta costuri foarte mari din partea furnizorilor de IP.

RISC-V este un set de instrucțiuni deschis, disponibil în baza unei licențe Berkeley Software Distribution (BSD). Proiectanții pot utiliza sau crea orice IP care implementează setul de instrucțiuni RISC-V, fără a plăti redevențe sau licențe pentru utilizarea setului de instrucțiuni. Extinderile standard ale setului de instrucțiuni au fost “înghețate”, ceea ce înseamnă că software-ul scris în viitor va putea utiliza întotdeauna aceste extensii standardizate, așa cum există în prezent.

Deoarece setul de instrucțiuni este deschis și există destul spațiu pentru cod operațional, proiectanții pot alege să extindă setul de instrucțiuni pentru a se potrivi exact nevoilor sistemului lor cu propriile instrucțiuni personalizate. De exemplu, dacă o anumită secvență de instrucțiuni apare foarte frecvent în codul creat pentru o anumită aplicație, proiectantul poate alege să creeze o nouă instrucțiune personalizată pentru a implementa secvența utilizată frecvent.

Proiectantul poate crea o logică suplimentară pentru ca IP-ul microprocesorului să implementeze noua instrucțiune rapid și eficient. Acest lucru poate oferi un spor semnificativ de performanță și poate reduce spațiul de cod pentru codul executabil. Înainte de apariția RISC-V, astfel de modificări ale soft-ului IP al procesorului erau disponibile doar pentru organizațiile care dețineau licențe arhitecturale, care sunt, de obicei, prohibitive din punct de vedere al costurilor.

Multe programe din sectorul apărării necesită utilizarea de componente electronice și IP încorporat provenite de la furnizori de încredere. Există foarte puține produse care îndeplinesc această cerință. Având un IP disponibil pentru inspecție în format HDL, este util pentru că permite proiectantului sau clientului final să valideze faptul că IP-ul conține doar codul necesar pentru a implementa funcția dorită. De asemenea, asigură clientul final al echipamentului că IP-ul este sigur pentru utilizarea în sistemele aerospațiale și de apărare.

Inspecția codului HDL poate contribui, de asemenea, la validarea proprietății intelectuale soft pentru aplicații critice din punct de vedere al siguranței, cum ar fi sistemele de aviație comercială, care sunt supuse unor proceduri riguroase privind certificarea navigabilității.

Ecosistemul RISC-V este în continuă expansiune. Prin inițiativa Mi-V, Microsemi oferă o suită cuprinzătoare de instrumente și resurse de proiectare dezvoltate intern și de numeroase părți terțe pentru a sprijini pe deplin proiectele RISC-V. Ecosistemul Mi-V are ca scop creșterea gradului de adoptare a RISC-V ISA și a familiei de produse CPU soft de la Microsemi.

Concluzie

RISC-V poate ajuta proiectanții din domeniul militar și aerospațial, care se confruntă cu provocările legate de reducerea la minimum a consumului de putere, a costului listei de materiale (BOM) și a spațiului de pe placa de circuit, permițând optimizarea setului de instrucțiuni cu scopul de a oferi cea mai eficientă implementare pentru fiecare aplicație în parte. Mai mult, proiectanții de sisteme din domeniul aerospațial și al apărării pot îndeplini cerințele de inspectabilitate cu ajutorul RISC-V.

Autor: Ken O’Neill,

Director de marketing al departamentului ‘Space and aviation’ la Microsemi, o companie Microchip Technology

Microchip Technology | https://www.microchip.com